Comprehensive Curriculum

Learn channel modeling, signal impairments, equalization techniques (FFE/DFE), clock-data recovery, and high-speed link analysis.

Practical Applications

Gain insight into real-world SerDes architectures, silicon implementation trade-offs, and performance limits in high-speed communication ICs.

Expert Guidance

Understand architectural decisions, modeling assumptions, and implementation constraints used in modern SerDes designs.

About the Course

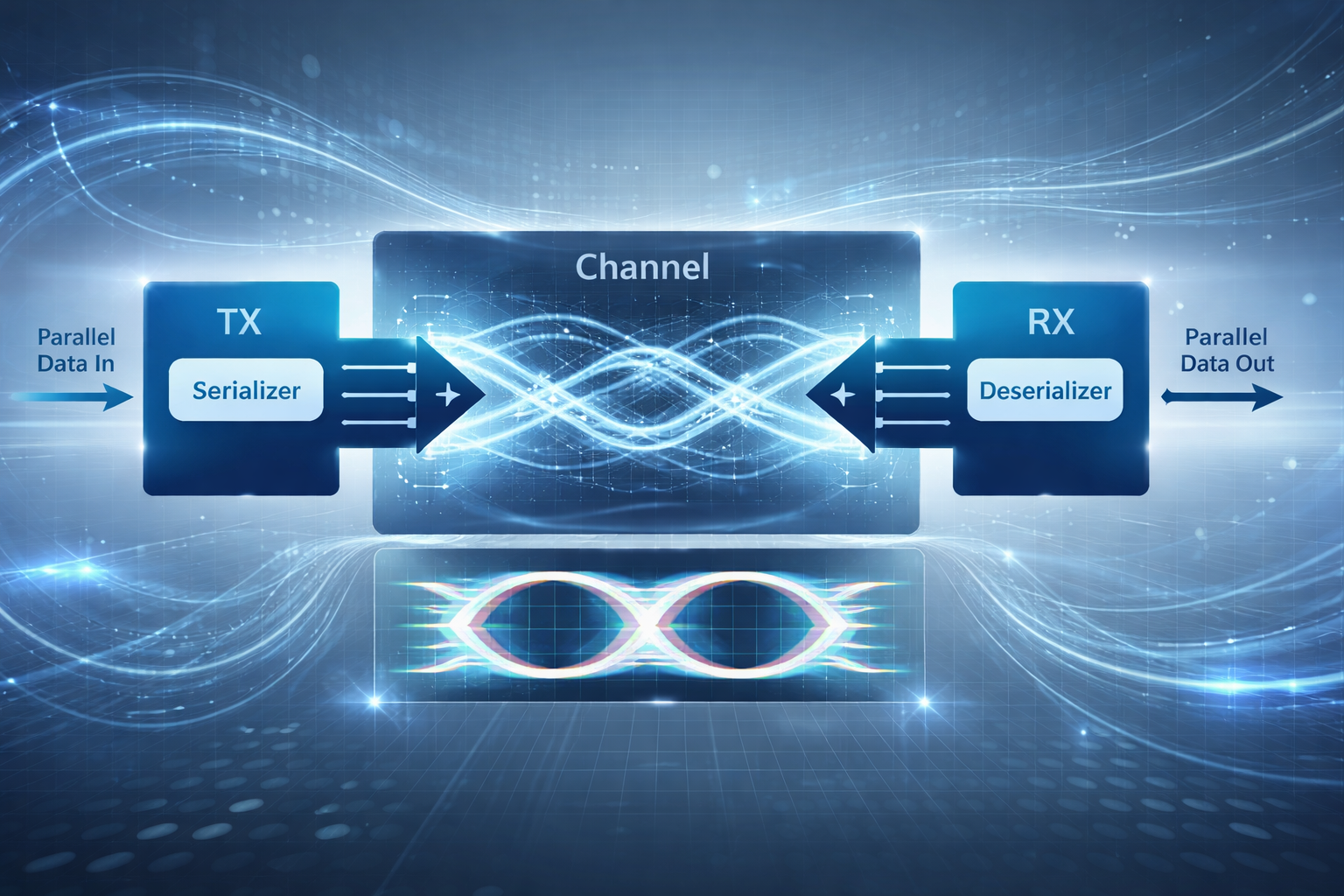

This course provides a structured and in-depth introduction to high-speed Serializer/Deserializer (SerDes) architectures used in modern communication integrated circuits. Students will study channel modeling, signal impairments, equalization techniques (including FFE and DFE), and clock-data recovery (CDR) systems, with a strong focus on architectural trade-offs and design intuition. The course is designed for senior undergraduate and graduate students, as well as practicing engineers, seeking a solid foundation for advanced work in high-speed link design, communication IC development, or related research areas.

Course Instructor

Dr. Juan Bonetti PhD-level instructor with extensive experience in high-speed serial links, SerDes architectures, and communication system modeling. This course is based on academic and industry-oriented material covering channel modeling, equalization techniques, and clock-data recovery, developed for advanced engineering education.

Course Curriculum

-

1

Welcome & Course Orientation

-

(Included in full purchase)

Course roadmap: TX/RX blocks and the SerDes link

-

(Included in full purchase)

-

2

Introduction & Channel Modeling

-

(Included in full purchase)

Understanding Channel Models

-

(Included in full purchase)

Intersymbol Interference and Mitigation

-

(Included in full purchase)

Quiz – Unit 1: SerDes Fundamentals and Channel Effects

-

(Included in full purchase)

-

3

Equalization Techniques

-

(Included in full purchase)

Feed-Forward Equalization (FFE)

-

(Included in full purchase)

Decision-Feedback Equalization (DFE)

-

(Included in full purchase)

-

4

Detection Algorithms and Performance

-

(Included in full purchase)

Adaptive Algorithms for SerDes

-

(Included in full purchase)

Maximum Likelihood Sequence Detection (MLSD)

-

(Included in full purchase)

-

5

Clock and Data Recovery Techniques

-

(Included in full purchase)

Designing CDR Systems

-

(Included in full purchase)

Evaluating Performance Trade-offs

-

(Included in full purchase)

Student Reviews

Testimonials build trust — fast. Edit this section to show how your product is making a difference and help your audience purchase with confidence.

This course provides a rare balance between mathematical rigor and architectural intuition. The treatment of channel modeling, FFE/DFE equalization, and CDR design helped me connect abstract models with real SerDes design decisions.

Córdoba, Arg

What sets this course apart is its focus on architectural trade-offs. It doesn’t just explain how SerDes blocks work — it explains why certain design choices are made in real silicon implementations.

Córdoba, Arg

Dr. Bonetti’s explanations reflect deep experience in both academic research and industry-oriented design. The material goes well beyond textbooks and addresses the realities of modern high-speed links.

Celero's Engineer

Unlock Your Potential

Enroll now to gain valuable insights into high-speed SerDes architectures and advance your career in electronics and telecommunications.